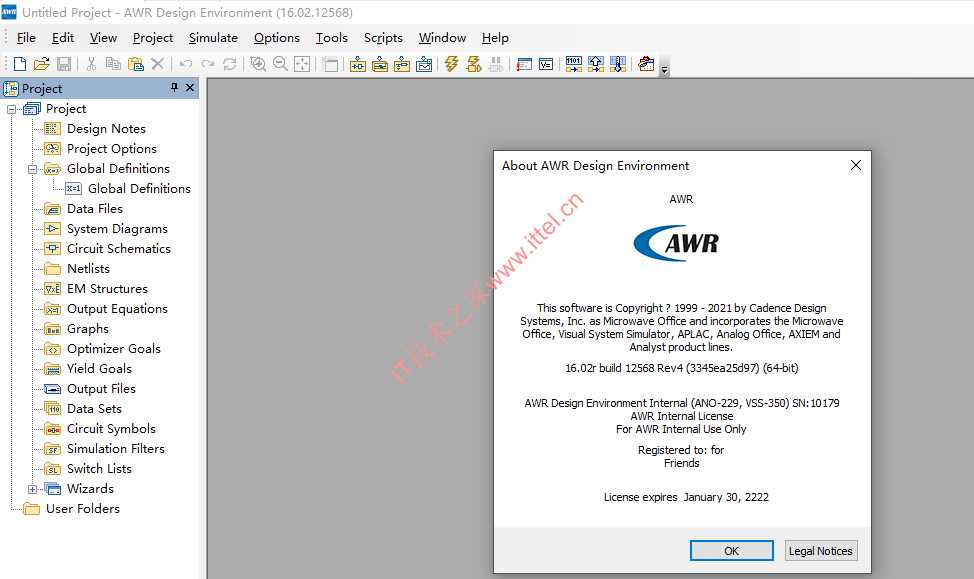

AWR Design Environment 16.02R 破解版

AWR Design Environment是由美国Cadence DesignSystems楷登电子公司推出的一款射频/微波电子设计自动化(EDA)工具,其EDA产品广泛用于手机,卫星通信系统和其他无线通信电子产品的设计与仿真。应用AWR产品进行设计,工程师可以快速开发出高技术含量,稳定可靠的新产品,大幅提高设计效率,降低成本。

目录

AWR Design Environment 软件特点

- 强大的

将概念转化为真正的射频/微波组件,针对性能进行优化,并准备好轻松集成到第一次正确的多结构系统中 - 有见地

通过紧密耦合的电磁 (EM) 和热分析捕获真正的 RF 系统性能,知识兔以解决大型复杂结构和发热 RF 功率应用 - 连接的

可嵌入且可重复使用的 Cadence Microwave Office® 电路设计软件 IP 开创了前所未有的跨平台工作流程新时代,知识兔适用于芯片、封装、电路板和模块设计的 Allegro 和 Virtuoso 平台 - 并行远程仿真

作业调度程序现在支持多个同时进行的远程队列,使设计人员能够在本地或远程并行运行长电路仿真或优化作业。EM 结构现在支持按文档远程队列选择,并且知识兔 Cadence AXIEM® 平面 EM 和 Analyst™ 3D 有限元方法 (FEM) 模拟都可以在远程 Linux 集群上运行。 - 动态空洞和自动网络连接提取

Microwave Office 软件中新的动态空洞布局模式会自动为各种绘图层添加布局形状和网络之间的间隙,并由布局过程文件 (LPF) 中指定的约束规则定义。例如,知识兔可以为通过接地或信号平面布线的信号走线自动添加间隙。额外的网络管理功能有助于识别布局和原理图中的网络对象,新的连接模式可实现形状与重叠网络的自动关联。 - 版本控制

版本控制管理组设计项目,允许对采用多种不同技术的复杂多功能设计进行组设计数据管理。当多个用户在版本控制数据库或中央存储库中编辑同一文件时,它还可以防止无意的文件覆盖。 - 布局走线互连建模

Cadence Visual System Simulator™ (VSS) 通信和雷达系统设计软件中的新互连 (INTERCONN) 系统模块对传输线损耗、阻抗失配和耦合的影响进行建模。该模块具有五种不同的操作模式,知识兔以促进设计流程,知识兔从布局的粗略估计开始,到在 EM 仿真中使用最终 PCB 布局走线。 - 单纯形优化器

具有可变步长的 Microwave Office 软件中增强的单线程和并行单纯形优化器比以前的单纯形优化器分享了更大的灵活性,使它们更广泛地适用和/或抵抗局部最小值。 - 射频放大器功率饱和度和倍频器建模

对 VSS 软件在饱和状态下对 RF 放大器建模的改进现在可以生成更平滑的功率输出与功率输入曲线。这些改进适用于时域、RF 预算分析和 RF Inspector (RFI) 模拟。此外,VSS 软件的行为倍频器模型已针对饱和输出功率和杂散电平进行了改进,在时域、RF 预算分析和 RFI 仿真之间产生了密切的一致性。预测性能对输入功率变化不太敏感,与物理倍频器设备的行为相匹配。

AWR Design Environment 安装激活

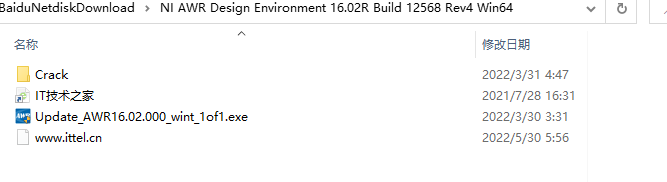

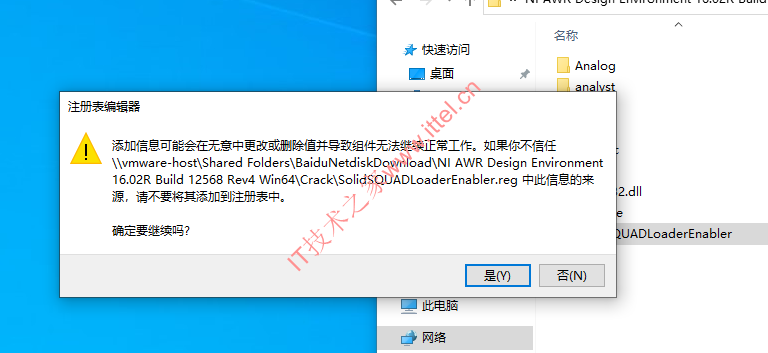

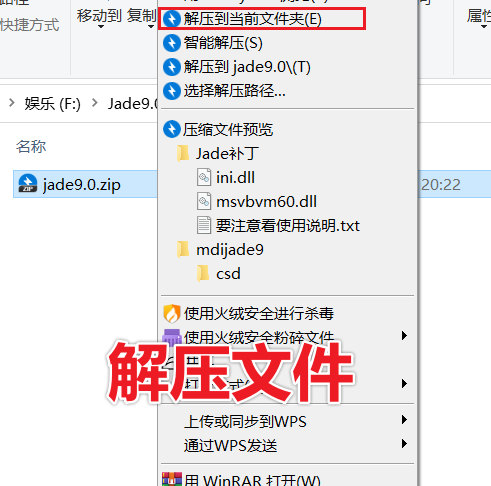

1、知识兔下载解压

2、右键管理员身份安装AWR Design Environment;

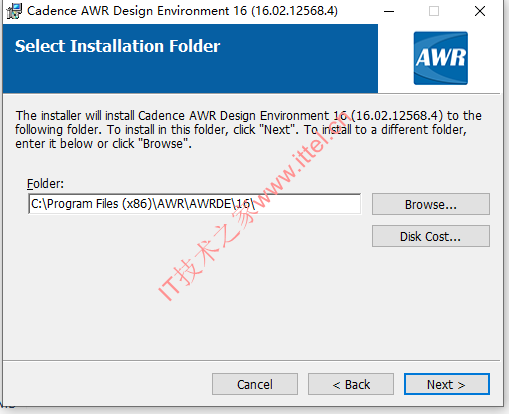

2、安装完成后,复制Crack内所有文件到软件安装目录替换原文件

默认安装路径:C:\Program Files (x86)\AWR\AWRDE\16\

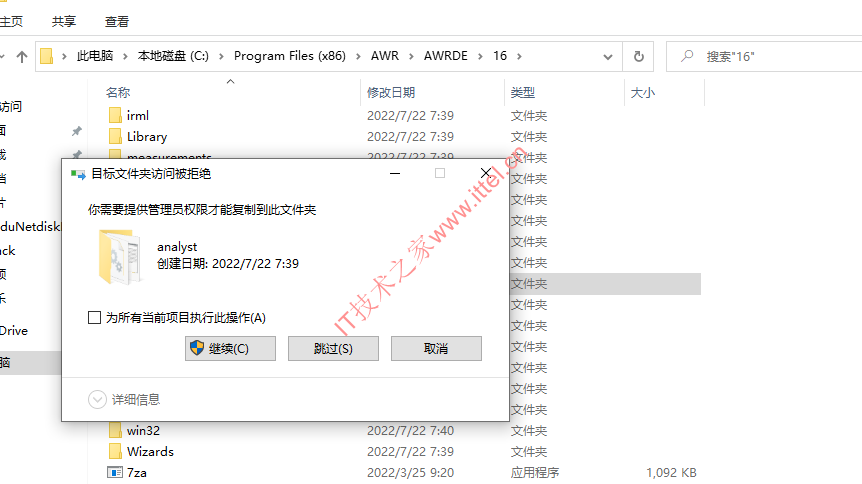

3、知识兔双击运行SolidSQUADLoaderEnabler.reg导入注册表信息;

4、安装完成,哎就很棒

下载仅供下载体验和测试学习,不得商用和正当使用。